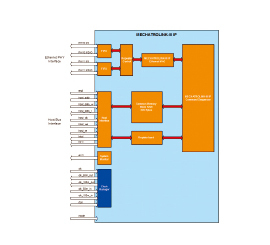

- MECHATROLINK-Ⅲ Master / Slave IP core

-

Peripheral Devices Built-in parts (ASIC etc)

-

MECHATROLINK Spec

M-II M-III M-4

Tokyo Electron Device Ltd.Updated on:Apr 4, 2019

MECHATROLINK-Ⅲ is a communication standard meets the demands of the motion field network market that required higher transmission speed, transmission cycle, transmission distance, maximum slave number, more than ever.

By adopting this IP core provided by Tokyo Electron Device Co., Ltd. for Xilinx's FPGA enables to reduce number of parts, development cost and development period greatly.

- Master function or Slave function

- Built-in CPU in FPGA enables to perform intelligent function using RTOS with one chip

- Synchronized to a clock of up to 66 MHz, connectable to a high-speed synchronous bus such as PCI without reduced throughput

Specification

| Item | Specifications |

|---|---|

| Target FPGA | Xilinx Spartan®-6 LX FPGA / Spartan-6 LXT FPGA / Zynq®-7000 SoC |

| Network Interface | MECHATROLINK-Ⅲ Network ×2 port (MⅡ I/F 100Mbps Full Duplex designated) |

| Host Interface | 32bit shared memory interface / 32bit register interface |

| Host Interrupt | 2 level Interrupt request output |

| Host Interface Byte Order | Little endian |

| Product Type | TIP-ML3MST-S6/7Z-PROJ (MECHATROLINK-Ⅲ Master Dedicated IP) TIP-ML3SLV-S6/7Z-PROJ (MECHATROLINK-Ⅲ Slave Dedicated IP) |

Attention

- To purchase this LSI, it is necessary to join the MECHATROLINK Members Association (MMA) with Board, Executive, Regular Membership.

Contact Information

Tokyo Electron Device Ltd.

| TOKYO ELECTRON DEVICE LIMITED | Yokohama East Square 1-4, Kinko-cho, Kanagawa-ku, Yokohama City, Kanagawa 221-0056, Japan TEL: +81-45-443-4034 FAX: +81-45-443-4059 |

URL:http://www.inrevium.com/product/industry/tip-ml3mst-proj.html